Data sheet acquired from Harris Semiconductor

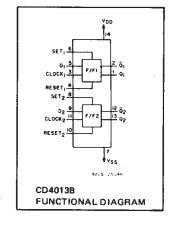

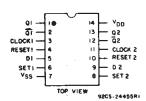

# CMOS Dual 'D'-Type Flip-Flop

High-Voltage Types (20-Volt Rating)

■ CD40138 consists of two identical, independent data-type flip-flops. Each flip-flop has independent data, set, reset, and clock inputs and Q and Q outputs. These devices can be used for shift register applications, and, by connecting Q output to the data input, for counter and toggle applications. The logic level present at the D input is transferred to the Q output during the positive-going transition of the clock pulse. Setting or resetting is independent of the clock and is accomplished by a high level on the set or reset line, respectively.

The CD4013B types are supplied in 14-lead hermetic dual-in-line ceramic packages (D and F suffixes), 14-lead dual-in-line plastic packages (E suffix), and in chip form (H suffix).

# CD4013B Types

#### Features:

- Set-Reset capability

- Static flip-flop operation retains state indefinitely with clock level either "high" or "low"

- Medium-speed operation 16 MHz (typ.) clock toggle rate at 10V

- Standardized symmetrical output characteristics

- 100% tested for quiescent current at 20 V

- Maximum input current of 1 µA at 18 V over full package temperature range;

100 nA at 18 V and 25°C

- Noise margin (over full package temperature range): 1 V at V<sub>DD</sub>=5 V

2 V at V<sub>DD</sub>=10 V

2.5 V at V<sub>DD</sub>=15 V

- 5-V, 10-V, and 15-W parametric ratings

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

#### Applications:

Registers, counters, control circuits

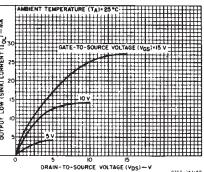

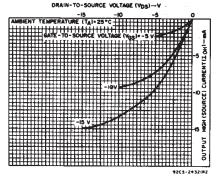

Fig. 1 — Typical output low (sink) current characteristics.

# RECOMMENDED OPERATING CONDITIONS

At  $T_A = 25^{\circ}$ C, Except as Noted. For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges:

| CHARACTERISTIC                                                                   | V <sub>DD</sub> | L    | UNITS    |        |  |

|----------------------------------------------------------------------------------|-----------------|------|----------|--------|--|

| on Anna Children                                                                 | (V)             | MIN. | MAX.     | Joints |  |

| Supply-Voltage Range<br>(For T <sub>A</sub> = Full Package<br>Temperature Range) | _               | 3    | 18       | V      |  |

| Data Setup Time t <sub>S</sub>                                                   | 5               | 40   | <u> </u> |        |  |

|                                                                                  | 10              | 20   | _        | ns     |  |

|                                                                                  | 15              | 15   | _        |        |  |

| Clock Pulse Width t <sub>W</sub>                                                 | 5               | 140  | -        |        |  |

|                                                                                  | 10              | 60   | _        | ns     |  |

|                                                                                  | 15              | 40   |          |        |  |

| Clock Input Frequency f <sub>CL</sub>                                            | 5               |      | 3.5      |        |  |

|                                                                                  | 10              | dc   | 8        | MHz    |  |

|                                                                                  | 15              |      | 12       |        |  |

| Clock Rise or Fall Time<br>t <sub>r</sub> CL,* t <sub>f</sub> CL                 | 5               | -    | 500      |        |  |

|                                                                                  | 10              | -    | 30       | μs     |  |

|                                                                                  | 15              | _    | 6        |        |  |

| Set or Reset Pulse Width                                                         | 5               | 180  | _        |        |  |

|                                                                                  | 10              | 80   | _        | ns     |  |

|                                                                                  | 15              | 50   | -        |        |  |

<sup>\*</sup>If more than one unit is cascaded in a parallel clocked operation, t<sub>r</sub>CL should be made less than or equal to the sum of the fixed propagation delay time at 15 pF and the transition time of the output driving stage for the estimated capacitive load.

Fig. 2 — Minimum output low (sink)

current characteristics.

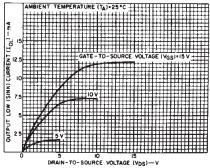

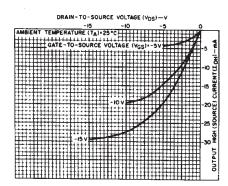

Fig. 3 — Typical output high (source) current characteristics.

# CD4013B Types

#### STATIC ELECTRICAL CHARACTERISTICS

| CHARAC-<br>TERISTIC                       |                       | CONDITIONS             |                 | LIMITS AT INDICATED TEMPERATURES (°C) |       |       |         |       |             | UNITS |     |

|-------------------------------------------|-----------------------|------------------------|-----------------|---------------------------------------|-------|-------|---------|-------|-------------|-------|-----|

|                                           | ν <sub>ο</sub><br>(v) | V <sub>IN</sub><br>(V) | V <sub>DD</sub> | 55                                    | -40   | +85   | +125    | Min.  | +25<br>Typ. | Max.  |     |

| Quiescent                                 | _                     | 0.5                    | 5               | 1                                     | 1     | 30    | 30      | _     | 0.02        | 1     |     |

| Device                                    | _                     | 0,10                   | 10              | 2                                     | 2     | 60    | 60      | _     | 0.02        | 2     |     |

| Current                                   |                       | 0,15                   | 15              | 4                                     | 4     | 120   | 120     |       | 0.02        | 4     | μΑ  |

| I <sub>DD</sub> Max.                      | _                     | 0,20                   | 20              | 20                                    | 20    | 600   | 600     | _     | 0.04        | 20    | 1   |

| Output Low                                |                       |                        |                 |                                       |       |       | <b></b> |       | _           |       |     |

| (Sink)                                    | 0.4                   | 0,5                    | 5               | 0.64                                  | 0.61  | 0.42  | 0.36    | 0.51  | 1           | _     |     |

| Current,                                  | 0.5                   | 0,10                   | 10              | 1.6                                   | 1.5   | 1.1   | 0.9     | 1.3   | 2.6         | -     | 1   |

| IOL Min.                                  | 1.5                   | 0,15                   | 15              | 4.2                                   | 4     | 2.8   | 2.4     | 3.4   | 6.8         | -     | ۱۸  |

| Output High                               | 4.6                   | 0,5                    | 5               | -0.64                                 | -0.61 | -0.42 | -0.36   | -0.51 | -1          | _     | mA  |

| (Source)                                  | 2.5                   | 0,5                    | 5               | -2                                    | -1.8  | -1.3  | -1.15   | -1.6  | -3.2        | _     |     |

| Current,                                  | 9.5                   | 0,10                   | 10              | -1.6                                  | -1.5  | -1.1  | -0.9    | -1.3  | -2.6        |       |     |

| IOH Min.                                  | 13.5                  | 0,15                   | 15              | -4.2                                  | -4    | -2.8  | -2.4    | -3.4  | -6.8        | _     |     |

| Output Voltage:                           | _                     | 0.5                    | 5               |                                       | 0.0   | 15    |         | _     | 0           | 0.05  |     |

| Low-Level                                 | _                     | 0,10                   | 10              |                                       | 0.0   |       |         | _     | 0           | 0.05  |     |

| VOL Max.                                  | -                     | 0,15                   | 15              |                                       | 0.05  |       |         | -     | 0           | 0.05  | ١., |

| Output Volt-                              |                       |                        |                 |                                       |       |       |         | -     |             |       | V   |

| age:                                      | _                     | 0,5                    | 5               |                                       | 4.9   | 95    |         | 4.95  | 5           | _     |     |

| High-Level,                               | _                     | 0,10                   | 10              |                                       | 9.9   | 95    |         | 9.95  | 10          | -     |     |

| V <sub>OH</sub> Min.                      | _                     | 0,15                   | 15              |                                       | 14.   | 95    |         | 14.95 | 15          | -     |     |

| Input Low                                 | 0.5,4.5               | _                      | 5               |                                       | 1.    | 5     |         | _     | _           | 1.5   |     |

| Voltage,                                  | 1,9                   | -                      | 10              |                                       | 3     | }     |         | _     | _           | 3     |     |

| VIL Max.                                  | 1.5,13.5              | _                      | 15              |                                       | 4     |       |         | -     | _           | 4     | v   |

| Input High                                | 0.5,4.5               | _                      | 5               |                                       | 3.    | 5     |         | 3.5   | _           |       | ľ   |

| Voltage,                                  | 1,9                   |                        | 10              | 7                                     |       |       | 7       |       | _           |       |     |

| V <sub>IH</sub> Min.                      | 1.5,13.5              | _                      | 15              | 11                                    |       |       | 11      | -     | -           |       |     |

| Input<br>Current,<br>I <sub>IN</sub> Max. | _                     | 0,18                   | 18              | ±0.1                                  | ±0.1  | ±1    | ±1      | -     | ±10-5       | ±0.1  | μΑ  |

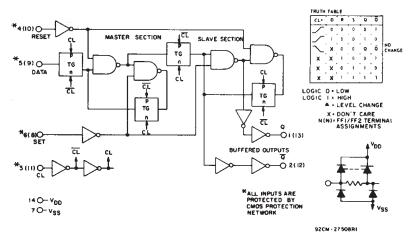

Fig. 7 - Logic diagram and truth table for CD4013B (one of two identical flip-flops).

Fig. 4 — Minimum output high (source) current characteristics.

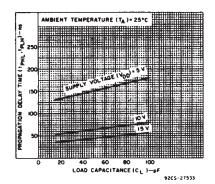

Fig. 5 — Typical propagation delay time vs. load capacitance (CLOCK or SET to O,CLOCK or RESET to \overline{\overline{O}}.

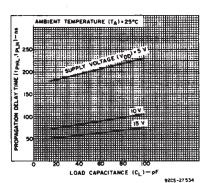

Fig. 6 — Typical propagation delay time vs. load capacitance (SET to  $\overline{Q}$  or RESET to Q.

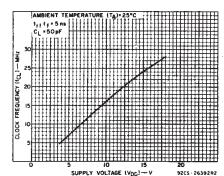

Fig. 8 — Typical maximum clock frequency vs. supply voltage.

# CD4013B Types

| MAXIMUM RATINGS, Absolute-Maximum Values:                                 |

|---------------------------------------------------------------------------|

| DC SUPPLY-VOLTAGE RANGE, (VDD)                                            |

| Voltages referenced to V <sub>SS</sub> Terminal)0.5V to +20V              |

| INPUT VOLTAGE RANGE, ALL INPUTS                                           |

| DC INPUT CURRENT, ANY ONE INPUT                                           |

| POWER DISSIPATION PER PACKAGE (PD):                                       |

| For T <sub>A</sub> = -55°C to +100°C                                      |

| For T <sub>A</sub> = +100°C to +125°C                                     |

| DEVICE DISSIPATION PER OUTPUT TRANSISTOR                                  |

| FOR TA = FULL PACKAGE-TEMPERATURE RANGE (All Package Types)               |

| OPERATING-TEMPERATURE RANGE (T <sub>A</sub> )                             |

| STORAGE TEMPERATURE RANGE (Tato)65°C to +150°C                            |

| LEAD TEMPERATURE (DURING SOLDERING):                                      |

| At distance 1/16 ± 1/32 inch (1.59 ± 0.79mm) from case for 10s max +265°C |

Fig. 9 – Typical power dissipation vs. frequency.

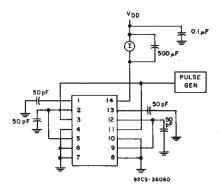

## TEST CIRCUITS

### **DYNAMIC ELECTRICAL CHARACTERISTICS**

At  $T_A$  = 25°C; Input  $t_r$ ,  $t_t$  = 20 ns,  $C_L$  = 50 pF,  $R_L$  = 20 k $\Omega$

| CHARACTERISTIC                          | TEST CONDITIONS     | LIMITS         |     |      | LINUTO |  |

|-----------------------------------------|---------------------|----------------|-----|------|--------|--|

| CHARACTERISTIC                          | V <sub>DD</sub> (V) | MIN. TYP.      |     | MAX. | UNITS  |  |

| Propagation Delay Time:                 | 5                   |                | 150 | 300  |        |  |

| Clock to Q or Q Outputs                 | 10                  | -              | 65  | 130  | ns     |  |

| t <sub>PHL</sub> , t <sub>PLH</sub>     | 15                  |                | 45  | 90   |        |  |

|                                         | 5                   | _              | 150 | 300  |        |  |

| Set to Q or Reset to Q t <sub>PLH</sub> | 10                  | -              | 65  | 130  | ns     |  |

|                                         | 15                  | _              | 45  | 90   |        |  |

|                                         | 5                   |                | 200 | 400  |        |  |

| Set to Q or Reset to Q t <sub>PHL</sub> | 10                  | <del>-</del> - | 85  | 170  | ns     |  |

|                                         | 15                  | _              | 60  | 120  |        |  |

|                                         | 5                   | _              | 100 | 200  |        |  |

| Transition Time tthL, ttlh              | 10                  | _              | 50  | 100  | ns     |  |

|                                         | 15                  | _              | 40  | 80   |        |  |

| Maximum Clock Input                     | 5                   | 3.5            | 7   |      |        |  |

| Frequency# fcL                          | 10                  | 8              | 16  | _    | MHz    |  |

|                                         | 15                  | 12             | 24  | _    |        |  |

| Minimum Clock Pulse Width               | 5                   | _              | 70  | 140  |        |  |

|                                         | 10                  | _              | 30  | 60   | กร     |  |

| tw                                      | 15                  | _              | 20  | 40   |        |  |

| Minimum Set or Reset Pulse              | 5                   |                | 90  | 180  |        |  |

| Width tw                                | 10                  |                | 40  | 80   | ns     |  |

|                                         | 15                  | _              | 25  | 50   | . *    |  |

| Minimum Data Setup Time ts              | 5                   |                | 20  | 40   |        |  |

|                                         | 10                  | _              | 10  | 20   | ns     |  |

|                                         | 15                  |                | 7   | 15   | 1      |  |

|                                         | 5                   |                | 2   | 5    |        |  |

| Minimum Data Hold Time t <sub>H</sub>   | 10                  | _              | 2   | 5    | ns     |  |

|                                         | 15                  | _              | 2   | 5    | Ì      |  |

| Clock Input Rise or Fall Time           | 5                   |                | _   | 500  |        |  |

| t <sub>r</sub> CL, t <sub>r</sub> CL    | 10                  | _              | -   | 30   | μs     |  |

|                                         | 15                  | _              | –   | 6    |        |  |

| Input Capacitance CiN                   | Any Input           | _              | 5   | 7.5  | pF     |  |

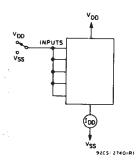

Fig. 10 - Quiescent device current.

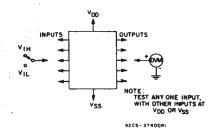

Fig. 11 - Input voltage.

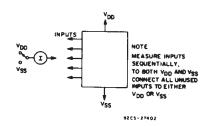

Fig. 12 - Input current.

# CD4013B Types

TERMINAL ASSIGNMENT

Fig. 13—Dynamic power dissipation test circuit.

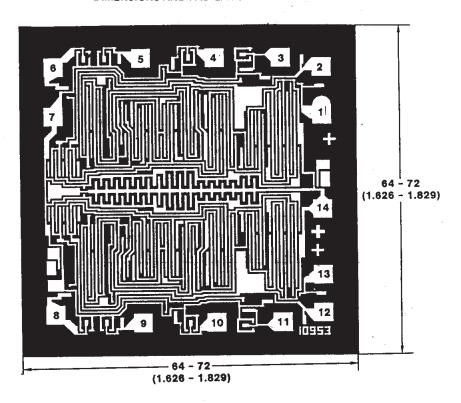

### **DIMENSIONS AND PAD LAYOUT FOR CD4013BH**

Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated. Grid graduations are in mils  $(10^{-3} \, \text{inch})$ .

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated