#### 8-BIT 30MSPS HIGH-SPEED CMOS A/D CONVERTER

The KAD0228 is a CMOS 8-bit A/D converter for video applications. It is a two-step ping-pong A/D converter consisting of reference resistor matrix, coarse 4-bit ADC and fine 4-bit ADC. Its maximum conversion rate is 30MSPS and supply voltage is 5V single.

#### **FEATURES**

• Resolution: 8-bit

Differential Linearity Error: ± 0.6 LSB Typ.

Maximum Conversion Rate: 30MSPS

Sample and Hold Function Included

• Low power consumption: Less than 90mW (At 20MSPS Typ.)

(Reference Current Excluded)

• Digital Input: CMOS level

• 3-state TTL compatible output

. Built-in Reference voltage bias circuit

• Reference Impedance: 300Ω • Power supply: 5V single

#### ORDERING INFORMATION

| Device |           | Package | Temperature Range |  |  |

|--------|-----------|---------|-------------------|--|--|

|        | KAD0228ED | 24 SOP  | 0~+70°C           |  |  |

#### TYPICAL APPLICATIONS

- PC or computer based video signal processing such as multi-media, frame-grabber, scanner, etc.

- General purpose video applications including camcorder, digital video (TV/VCR), broadcasting and studio equipments.

- · Medical electronics such as ultra-sound, imaging.

- · High speed instrumentations such as digital scope, transit recorder, radar.

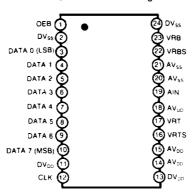

## **PIN DESCRIPTION**

| Pin No. Symbol I/O |           | I/O | Description                                                            |  |  |

|--------------------|-----------|-----|------------------------------------------------------------------------|--|--|

| 1                  | OEB       | 1   | 3-state output enable                                                  |  |  |

|                    |           |     | 3-state when OEB = V <sub>DD</sub> , enable when OEB = V <sub>SS</sub> |  |  |

| 2                  | DVss      | _   | Digital ground for digital output buffer                               |  |  |

| 3                  | DATA 0    | 0   | Digital output data (LSB)                                              |  |  |

| 4                  | DATA 1    | 0   | Digital output data                                                    |  |  |

| 5                  | DATA 2    | 0   | Digital output data                                                    |  |  |

| 6                  | DATA 3    | 0   | Digital output data                                                    |  |  |

| 7                  | DATA 4    | 0   | Digital output data                                                    |  |  |

| 8                  | DATA 5    | 0   | Digital output data                                                    |  |  |

| 9                  | DATA 6    | Ο   | Digital output data                                                    |  |  |

| 10                 | DATA 7    | 0   | Digital output data (MSB)                                              |  |  |

| 11                 | $DV_{DO}$ | _   | Digital supply for digital output buffer                               |  |  |

| 12                 | CLK       | 1   | CMOS digital clock input                                               |  |  |

| 13                 | $DV_DO$   | _   | Digital supply for digital interior circuitry                          |  |  |

| 14                 | $AV_{DD}$ | _   | Analog supply for comparator, reference resistor switch                |  |  |

| 15                 | AVDD      |     | Same as pin No. 14                                                     |  |  |

| 16                 | VRTS      | 0   | Internal self-biased reference top.                                    |  |  |

|                    |           |     | Shorted with VRT pin (17), generates 2.6 volts.                        |  |  |

| 17                 | VAT       | l I | Reference resistor top side                                            |  |  |

| 18                 | AVDD      |     | Same as pin No. 14                                                     |  |  |

| 19                 | AIN       | 1   | Analog input                                                           |  |  |

| 20                 | AVss      | _   | Analog ground for comparator, reference resistor switch                |  |  |

| 21                 | AVss      | _   | Same as pin No. 20                                                     |  |  |

| 22                 | VRBS      | 0   | Internal self-biased reference bottom.                                 |  |  |

|                    |           |     | Shorted with VRB pin (23), generates 0.6 volts.                        |  |  |

| 23                 | VRB       | 1   | Reference resistor bottom side                                         |  |  |

| 24                 | $DV_{ss}$ | -   | Digital ground for digital interior circuitry                          |  |  |

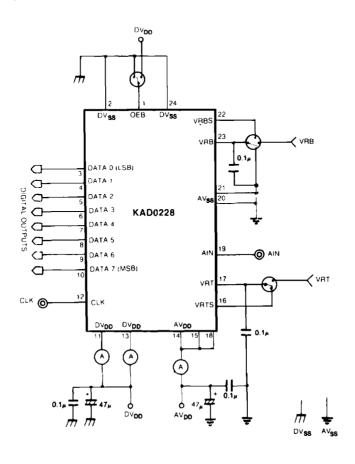

# PIN CONFIGURATION (24 SOP)

(Top View)

## ABSOLUTE MAXIMUM RATINGS (Note 1 & 2)

| Characteristics             | Symbol           | Value                              | Unit |

|-----------------------------|------------------|------------------------------------|------|

| Supply voltage              | V <sub>DD</sub>  | - 0.5 to 7.0                       | V    |

| Analog Input Voltage        | AIN              | V <sub>ss</sub> to V <sub>pp</sub> | V    |

| Reference Input Voltage     | VRT, VRB         | V <sub>ss</sub> to V <sub>oo</sub> | V    |

| Storage Temperature Range   | T <sub>stq</sub> | - 55 to + 125                      | °C   |

| Operating Temperature Range | Topr             | - 20 to + 75                       | °C   |

| ESD Susceptibility (Note 3) | V <sub>esd</sub> | > ± 1500                           | V    |

Note 1: ABSOLUTE MAXIMUM RATINGS are those values beyond which the device may be damaged permanently. Normal operation is not guaranteed at or above these extremes.

Note 2: All voltages are measured with respect to the Vss voltage level otherwise specified

Note 3: 100pF discharged through a 1.5kΩ resistor (Human body model).

#### RECOMMENDED OPERATING CONDITIONS (Note 4)

| Characteristics                                        | Symbol                                                                     | Min      | Тур        | Max  | Unit |

|--------------------------------------------------------|----------------------------------------------------------------------------|----------|------------|------|------|

| Supply Voltage                                         | AV <sub>DD</sub> - AV <sub>SS</sub><br>DV <sub>DD</sub> - DV <sub>SS</sub> | 4.75     | 5.0        | 5.25 | V    |

| Supply Voltage Difference                              | AV <sub>DD</sub> - DV <sub>DD</sub>                                        | - 0.1    | 0.0        | 0.1  | V    |

| Reference Input Voltage (Note 5)                       | VRB<br>VRT                                                                 | 0 —      | 0.6<br>2.6 | 2.8  | V    |

| Analog Input Voltage                                   | AIN                                                                        | VRB      | _          | VRT  | V    |

| Clock High Time<br>Clock Low Time                      | t <sub>pwr</sub> +                                                         | 15<br>15 | _          |      | ns   |

| Digital Input "L" Voltage<br>Digital Input "H" Voltage | V <sub>Ik</sub><br>V <sub>IH</sub>                                         | 4.0      | _          | 1.0  | v    |

| Operating Temperature                                  | Topr                                                                       | 0        | _          | 70   | °C   |

Note 4. It is strongly recommended that all the supply pins (AV<sub>DD</sub>, DV<sub>DD</sub>) be powered from the same source. Note 5. The value of (VRB  $\times$  VRT)can be moved to the up side (2  $\sim$  4V), but characteristics can't be guaranteed.

## STATIC ELECTRICAL CHARACTERISTICS

(Converter Specifications:  $AV_{\rm DD}$  =  $DV_{\rm DD}$  = 5V,  $AV_{\rm SS}$  =  $DV_{\rm SS}$  = 0V, Ta = 25°C, VRB = 0.6V, and VRT = 2.6V unless otherwise specified)

| Characteristics                                          | Symbol       | Test Conditions                                                                        | Min         | Тур            | Max            | Unit |

|----------------------------------------------------------|--------------|----------------------------------------------------------------------------------------|-------------|----------------|----------------|------|

| Reference Current                                        | IREF         | VRT = 2.6V, VRB = 0.6V                                                                 | 5.0         | 6.7            | 10             | mA   |

| Reference Resistance                                     | RREF         |                                                                                        | 200         | 300            | 400            | Ω    |

| Internal Bias                                            | VRBS<br>VREF | Short VRT and VRTS<br>Short VRB and VRBS                                               | 0.55<br>1.9 | 0.60<br>2.0    | 0.65<br>2.1    | v    |

| Digital Input Low Current                                | IIL          | $V_{\rm DD} = 5.25$ , VIL = $V_{\rm SS}$                                               | <b>1</b> —  |                | 1              | μA   |

| Digital Input High Current                               | IIH          | $V_{\rm DD} = 5.25$ , VIH = $V_{\rm DD}$                                               | 1 -         | _              | 1              | μΑ   |

| Digital Output Current<br>(Output Enable)                | IOL<br>IOH   | $V_{DD} = 4.75$ , $VOL = 0.4V$<br>$VOH = V_{DD} - 0.5V$<br>OEB = VSS                   | 3.5         | _              | _              | mA   |

| Digital Output Current<br>(Output High Imp.)             | IOZL<br>IOZH | $V_{\text{DD}} = 5.25$ , $VOL = VSS$<br>$VOH = V_{\text{DD}}$<br>$OEB = V_{\text{DD}}$ |             |                | 16<br>16       | uA   |

| Offset Voltage Error                                     | EOT<br>EOB   | $V_{DD} = 5.0$ ,<br>VRT = 2.6V, VRB = 0.6V                                             | 0           | - 25<br>+ 20   | - 68<br>+ 40   | mV   |

| Differential Linearity Error<br>Integral Linearity Error | ELD<br>ELI   | $V_{OO} = 5.0$ ,<br>VRT = 2 6V, VRB = 0.6V                                             |             | ± 0.6<br>± 0.8 | ± 1.0<br>± 1.2 | LSB  |

#### DYNAMIC CHARACTERISTICS

(Converter Specifications:  $AV_{DD} = DV_{DD} = 5V$ ,  $AV_{SS} = DV_{SS} = 0V$ , Ta = 25°C, VRB = 0.6V, and VRT = 2.6V unless otherwise specified.)

| Characteristics                       | Symbol            | Test Conditions                            | Min | Тур | Max          | Unit |

|---------------------------------------|-------------------|--------------------------------------------|-----|-----|--------------|------|

| Maximum Conversion Rate               | fc                | AIN=0.6V to 2.6V,<br>1MHz sine wave        | 30  | -   | : <u> </u>   | MSPS |

| Dynamic Supply Current                | Ivoo              | F <sub>s</sub> =20MHz, AIN=NTSC ramp input | _   | 18  | 27           | mA   |

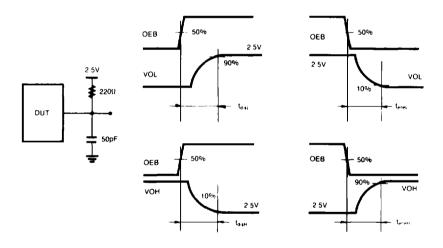

| Digital Output Data Delay<br>(Note 6) | l <sub>a</sub>    | OEB=V <sub>SS</sub>                        | _   | 18  | 30           | ns   |

| Digital Output Data Delay             | taisH             |                                            | -   | _   | 100          | ns   |

| (Output High Imp.)(Note 7)            | tass              |                                            |     | _   | 100          | 115  |

| Digital Data Valid Time               | t <sub>eneH</sub> |                                            | T - | I – | 100          |      |

| (Note 7)                              | t <sub>enel</sub> |                                            | _   |     | 100          | ns   |

|                                       |                   | CK=20MHz,                                  | Ţ   |     |              |      |

| Signal-to-Noise Ratio                 | SNR1              | AIN=1MHz sine wave                         | _   | 45  | _            | d₿   |

|                                       | SNR2              | 2MHz sine wave                             | _   | 45  | _            | dB   |

|                                       | SNR3              | 4MHz sine wave                             | -   | 41  | -            | dB   |

| Differentlal Phase                    | DP                | NTSC 20 IRE mod Ramp                       | _   | 0.7 | <del>-</del> | deg  |

| Differential Gain                     | DG                | signal, F <sub>s</sub> =14.3MSPS           | _   | 1.0 | _            | %    |

| Sampling Time Offset                  | t <sub>sto</sub>  |                                            | 1   | 5   | 10           | ns   |

Note 6:See "Delay Timing Diagram"

Note 7:See "3-State Putput Test Circuit and Timing diagram"

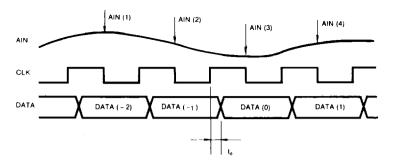

## **DELAY TIMING DIAGRAM**

#### I/O CHART

| Index | Analog Input (V)      | Digital Output |                 |

|-------|-----------------------|----------------|-----------------|

| 0     | ~ 0.6078125           | 00000000       |                 |

| 1     | 0.6078125 ~ 0.6156250 | 0000001        | VRB = 0.6V      |

| 2     | 0.6156250 ~ 0.6234375 | 0000010        | VRT = 2.6V      |

|       | <del></del>           | •••••          |                 |

| 126   | 1.5921875 ~ 1.6000000 | 01111111       | 1LSB = 7.8125mV |

| 127   | 1.6000000 ~ 1.6078125 | 10000000       |                 |

| 128   | 1.6078125 ~ 1.6156250 | 1000001        |                 |

|       |                       | *****          |                 |

| 254   | 2.5843750 ~ 2.5921875 | 11111110       |                 |

| 255   | 2.5921875 ~           | 11111111       |                 |

# 3-STATE OUTPUT TEST CIRCUIT AND TIMING DIAGRAM

#### **FUNCTIONAL DESCRIPTION**

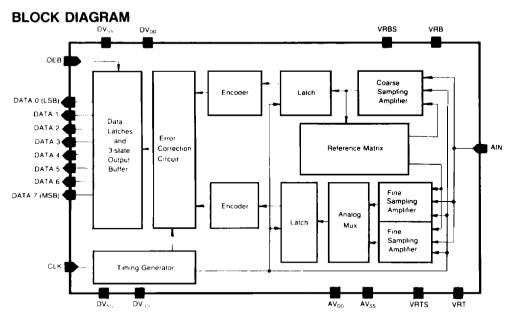

- KAD0228 is a two-step ping-pong A/D converter comprising 4-bit coarse ADC and fine ADC of 4.459 bit, approximately. Coarse ADC is composed of 15 auto zero comparators, and fine ADC has 22 sampling amplifier pairs of which the two sampling amplifier operate alternately in a ping-pong manner, and also has 22 analog MUXs and 22 latching comparators.

- 2. Using a CMOS auto zero comparator and switching 1 of 16 different sets of reference voltage to the fine sampling amplifier bank according to the coarse ADC state, the difficulties in implementing high accuracy (more than 8 bit) DAC was eliminated, thus low-power, high-performance, high-speed ADC was achieved. KAD0228 uses an averaging method to reduce the charge injection mismatch in the sampling switches, so the overall differential non-linearity error is enhanced.

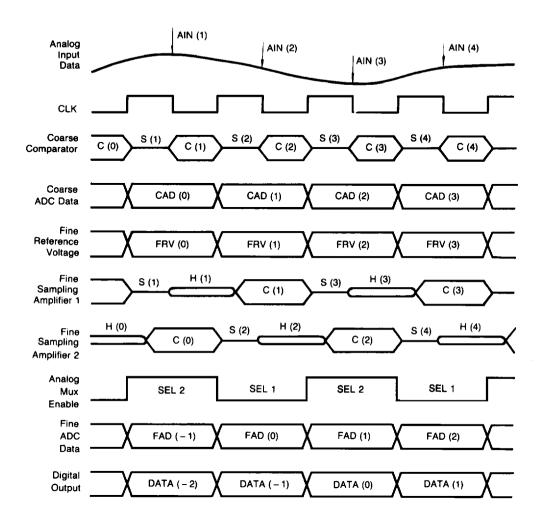

- 3. KAD0228 operates as follows (See Timing Diagram): During the first "H" cycle of external clock the analog input data is sampled and tracked, and the input is held from the falling edge of the CLK (the analog input is abbreviated to AIN in the timing diagram), which is compared with the 16-level coarse reference voltage and latched to result in data CAD. According to the coarse ADC data, the fine reference voltage FRV is set and fed to the fine sampling amplifier bank. This FRV voltage set is compared with the sampled analog input, and resulted in the fine sampling amplifier data. The fine sampling amplifier operates in a ping-pong style to reproduce the analog data with sufficiently large gain, and then MUXed to the latching comparators. Latching comparator bank generates the fine ADC data (FAD), which is used to generate the digital output (DATA) together with the CAD data. The overall pipeline delay is 2.5 clock.

- 4. KAD0228 has the correction scheme of the error which comes from the mismatch in the coarse ADC and the fine sampling amplifier offset. This error correction scheme can handle up to 3 LSBs, and hence helps enhance the differential linearity.

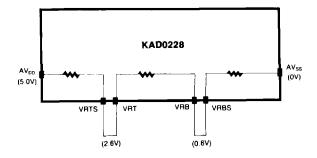

- 5. Inside KAD0228, reference resistors are placed between AV<sub>DD</sub> and VRTS, and between AV<sub>SS</sub> and VRBS so that VRTS and VRBS generate the 2.6V, and 0.6 Volt reference respectively. In order to utilize the internal self-biased reference voltage, the VRTS pin (16) is to be shorted with VRT pin (17) and the VRBS pin (22) is to be shorted with the VRB pin (23). It is not recommended to take advantage of the self-biased internal reference voltage in case of applying KAD0228 in a special system which offers high accuracy, though (See Reference Circuit Diagram).

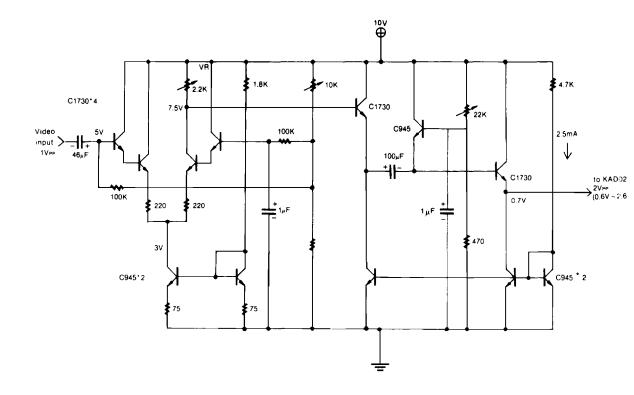

#### REFERENCE CIRCUIT DIAGRAM

#### **TIMING DIAGRAM**

## TEST CIRCUIT (Note 8)

Note  $8.AV_{0D}$  and  $DV_{0D}$  are needed to be out from common source. Make the distance between CLK source and CLK DUT pin as short as possible. Test circuit can be changed because of test equipment and test items.

# A/D Input Amplifier and Clamping Circuit